Product Summary

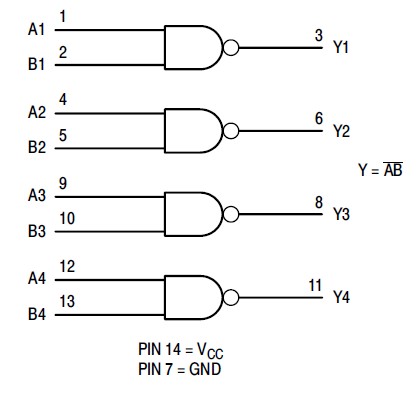

The 74HC00ADTEL is a Quad 2-Input NAND Gate. It is identical in pinout to the LS00. The 74HC00ADTEL inputs are compatible with Standard CMOS outputs; with pullup resistors, they are compatible with LSTTL outputs.

Parametrics

74HC00ADTEL absolute maximum ratings: (1)VCC DC Supply Voltage (Referenced to GND): -0.5 to + 7.0 V; (2)Vin DC Input Voltage (Referenced to GND): 0.5 to VCC + 0.5 V; (3)Vout DC Output Voltage (Referenced to GND): 0.5 to VCC + 0.5 V; (4)Iin DC Input Current, per Pin: ±20 mA; (5)Iout DC Output Current, per Pin: ±25 mA; (6)ICC DC Supply Current, VCC and GND Pins: ±50 mA; (7)PD Power Dissipation in Still Air: 750 mW; (8)Tstg Storage Temperature: -65 to + 150 ℃; (9)TL Lead Temperature, 1 mm from Case for 10 Seconds Plastic DIP, SOIC or TSSOP Package: 260 ℃.

Features

74HC00ADTEL features: (1)Pb-Free Packages are Available; (2)Output Drive Capability: 10 LSTTL Loads; (3)Outputs Directly Interface to CMOS, NMOS and TTL; (4)Operating Voltage Range: 2 to 6 V; (5)Low Input Current: 1 μA; (6)High Noise Immunity Characteristic of CMOS Devices; (7)In Compliance With the JEDEC Standard No. 7 A Requirements; (8)Chip Complexity: 32 FETs or 8 Equivalent Gates.

Diagrams

|

74HC |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT02 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT03 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT10 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT107 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT109 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))